# ProjectIC Based SoC Integration Workflow

SoC Integration is a challenging and important task that all hardware teams undertake on a regular basis.

A SoC is typically made up of series of IPs, each of which could also be a sub-system in its own right. The key role of integration is to accept new releases of the component IPs and/or sub-systems, verify whether these newer releases work in the context of the SoC.

The releases that are available for integration should have passed some quality control of their own - i.e. basic checks that ensure that the release that is available for integration satisfies a minimum quality level, and moves the SoC forward.

## **Integration Roles**

Integration roles can be defined as follows:

### Integrator

The key role in the integration flow is that of the integrator. The integrator decides how and when to pick up new releases of component IPs and sub-systems that are available.

As part of the integrator's role, she needs the following capabilities:

- Indication of when a new release of each of the component IPs is available for integration. This

information should be easily available.

- Quickly and seamlessly introduce any subset of the available releases into an existing workspace

the new SoC configuration under test

- Quickly and seamlessly revert any subset of the newly introduced releases from an existing workspace - tweak the new SoC configuration

- Launch the required tests in the workspace to qualify the configuration with new releases

- Easily capture the tested configuration as the new top-level configuration for the SoC release the SoC with new IPs after test

#### Contributor

Contributors are IP and sub-system owners that provide new releases to the integrator for integration. These new releases can be generated to fix bugs and/or add new features as required by the SoC.

As part of the Contributor's role, he needs the following capabilities:

- Generate a new release of an IP or sub-system after making the modifications required

- Guarantee the minimum quality level of these releases based on the commonly agreed terms for the team or SoC. This is done by testing the release in its context before notifying the integrator of the availability of a new release.

- An easy way to indicate the availability of a new release for integration

#### Consumer

Consumers of the SoC use qualified, integrator blessed versions for other flows - for example to run downstream flows like power analysis or synthesis. These users need the following capabilities:

- An SoC configuration that is known to have been qualified by the integrator

- An indication when a new version of the configuration has been qualified by the integrator.

### **Integration Flow**

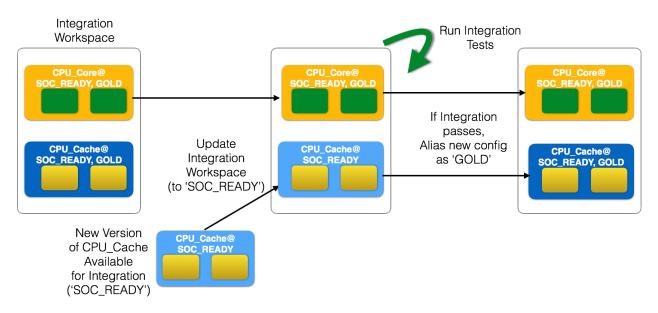

ProjectIC uses the notion of 'Moving Aliases' to implement the integration flow. An IP or subsystem release can be aliased with a string that has some meaning - for example, 'SOC\_READY' for a release that is SOC\_READY for integration, 'GOLD' for a integration qualified release - as a communication channel to accomplish integration.

In this example, we will use the 'SOC\_READY' alias for component IPs when they are SOC\_READY for integration, and a 'GOLD' alias when the integrator has blessed an IP as qualified after running her tests.

Additionally, we will use two top level SoC definitions for this flow:

1. the 'lib.soc\_integ' top level configuration (a <u>container</u> in ProjectIC terms) is used by the integrator to run her integration step. This top level configuration uses IPs at the 'SOC\_READY' alias, as shown:

2. the 'lib.soc\_top' top level configuration is used by consumers to pick up integrator qualified configurations. This top level configuration is shown below:

Some things to note in the above definitions:

- The coco.CPU\_Logic IP is not expected to change during this project. Hence, that particular IP is used at a fixed release (coco.CPU\_Logic@6). A container can include resource IPs and subsystems at both fixed releases or at moving aliases.

- When workspaces are built with these top levels, all the IPs dependencies of these sub-systems are also automatically brought into that workspace. Thus workspace status generally contain several more IPs than the ones included as direct resources in the top level.

• The top level includes 3 IPs, but each of these IPs is really a subsystem, which includes IPs of its own. ProjectIC understands hierarchy across all its functions, so this is never a limitation.

The integration flow is indicated in the diagram below.

Integration starts with the integrator creating a workspace with the 'soc integ' project.

As shown in the tree display above, the SoC uses two of its component IPs - coco.CPU\_Core and coco.CPU\_Cache - on an alias called 'SOC\_READY' . What this implies is that instead of fixing the versions of these IPs, the SoC will use the latest versions that are marked 'SOC\_READY'. Using these moving aliases is a critical communication mechanism between the contributors and the integrator.

The integrator can load this SoC into a workspace using the ProjectIC IP load command:

[integrator]% pi ip load lib.soc\_integ integ1

The 'integ1' directory now contains all the IPs and sub-systems of the SoC. These IPs and sub-systems are created as links to a common 'IP Cache' for speed and disk-space optimization. Please refer to ProjectIC documentation for more on the IP Cache. The snippet below shows the composition of this integration workspace as a set of links. Each directory is an IP in the listing.

IEC\_ARM\_coco.SY750 -> /mdx\_local/mdx\_data/bic\_shares/IEC\_ARM\_coco/SY750/TRUNK/5/IEC\_ARM\_coco.SY750

coco.CPU\_Cache -> /mdx\_local/mdx\_data/bic\_shares/coco/CPU\_Cache/TRUNK/GOLD/coco.CPU\_Cache

coco.CPU\_Core -> /mdx\_local/mdx\_data/bic\_shares/coco/CPU\_Logic/TRUNK/6/coco.CPU\_Core

coco.CPU\_Logic -> /mdx\_local/mdx\_data/bic\_shares/coco/CPU\_Logic/TRUNK/6/coco.CPU\_Logic

Memories.CS-TS28N-GS-1PSRM -> /mdx\_local/mdx\_data/bic\_shares/Memories/CS-TS28N-GS-1PSRM/TRUNK/5/Memories.CS-TS28N-GS-1PSRM/TRUNK/5/Memories.CS-TS28N-GS-1PSRM/TRUNK/5/Memories.CS-TS28N-GS-1PSRM/TRUNK/5/Memories.CS-TS28N-GS-1PSRM/TRUNK/5/Memories.CS-TS28N-GS-1PSRM/TRUNK/5/Memories.CS-TS28N-GS-1PSRM/TRUNK/5/Memories.CS-TS28N-GS-1PSRM/TRUNK/5/Memories.CS-TS28N-GS-1PSRM/TRUNK/5/Memories.CS-TS28N-GS-1PSRM/TRUNK/5/Memories.CS-TS28N-GS-1PSRM/TRUNK/5/Memories.CS-TS28N-GS-1PSRM/TRUNK/5/Memories.CS-TS28N-GS-1PSRM/TRUNK/5/Memories.CS-TS28N-GS-1PSRM/TRUNK/5/Memories.CS-TS28N-GS-1PSRM/TRUNK/5/Memories.CS-TS28N-GS-1PSRM/TRUNK/5/Memories.CS-TS28N-GS-1PSRM/TRUNK/5/Memories.CS-TS28N-GS-1PSRM/TRUNK/5/Memories.CS-TS28N-GS-1PSRM/TRUNK/5/Memories.CS-TS28N-GS-1PSRM/TRUNK/5/Memories.CS-TS28N-GS-1PSRM/TRUNK/5/Memories.CS-TS28N-GS-1PSRM/TRUNK/5/Memories.CS-TS28N-GS-1PSRM/TRUNK/5/Memories.CS-TS28N-GS-1PSRM/TRUNK/5/Memories.CS-TS28N-GS-1PSRM/TRUNK/5/Memories.CS-TS28N-GS-1PSRM/TRUNK/5/Memories.CS-TS28N-GS-1PSRM/TRUNK/5/Memories.CS-TS28N-GS-1PSRM/TRUNK/5/Memories.CS-TS28N-GS-1PSRM/TRUNK/5/Memories.CS-TS28N-GS-1PSRM/TRUNK/5/Memories.CS-TS28N-GS-1PSRM/TRUNK/5/Memories.CS-TS28N-GS-1PSRM/TRUNK/5/Memories.CS-TS28N-GS-1PSRM/TRUNK/5/Memories.CS-TS28N-GS-1PSRM/TRUNK/5/Memories.CS-TS28N-GS-1PSRM/TRUNK/5/Memories.CS-TS28N-GS-1PSRM/TRUNK/5/Memories.CS-TS28N-GS-1PSRM/TRUNK/5/Memories.CS-TS28N-GS-1PSRM/TRUNK/5/Memories.CS-TS28N-GS-1PSRM/TRUNK/5/Memories.CS-TS28N-GS-1PSRM/TRUNK/5/Memories.CS-TS28N-GS-1PSRM/TRUNK/5/Memories.CS-TS28N-GS-1PSRM/TRUNK/5/Memories.CS-TS28N-GS-1PSRM/TRUNK/5/Memories.CS-TS28N-GS-1PSRM/TRUNK/5/Memories.CS-TS28N-GS-1PSRM/TRUNK/5/Memories.CS-TS28N-GS-1PSRM/TRUNK/5/Memories.

The integrator can now query the workspace to find out if there are any newer releases available for integration. At this time, there are no new releases that are marked 'SOC READY' for integration.

[integrator]% pi workspace status -v

Workspace ID: 16

Directory: /home/vishal/workspaces/integ1

IP: lib.soc\_integ@4.TRUNK

Resources:

| - 1 | Name                       | ı | Expected Version | 1   | Local Version | ı | WS St | atus | ı | Server Status | 1 | Mode      | 1 |

|-----|----------------------------|---|------------------|-----|---------------|---|-------|------|---|---------------|---|-----------|---|

| - 1 | lib.soc_integ              | 1 | 4.TRUNK          | - 1 | 4.TRUNK       | 1 | 0     | ΙK   | l | OK            | 1 | Container | 1 |

| - 1 | IEC_ARM_coco.SY750         | 1 | 5.TRUNK          | - [ | 5.TRUNK       | 1 | 0     | ΙK   | l | OK            | 1 | Refer     | 1 |

| - 1 | Memories.CS-TS28N-GS-1PSRM | 1 | 5.TRUNK          | -   | 5.TRUNK       | 1 | 0     | ΙK   | l | OK            | 1 | Refer     | 1 |

| - 1 | coco.CPU_Cache             | 1 | SOC_READY.TRUNK  | - [ | 8.TRUNK       | 1 | 0     | ΙK   | l | OK            | 1 | Refer     | 1 |

| - 1 | coco.CPU_Core              | 1 | SOC_READY.TRUNK  | - [ | 8.TRUNK       | 1 | 0     | ΙK   | l | OK            | 1 | Refer     | 1 |

| - 1 | coco.CPU Loaic             | Ī | 6.TRUNK          | 1   | 6.TRUNK       | 1 | 0     | K    | L | OK            | 1 | Refer     | 1 |

A contributor can now generate a new release of an IP, and mark it 'SOC\_READY'. As part of the release, the contributor runs a quality check to make sure that the release meets the required quality criteria. These quality checks can be run automatically in the user's workspace as part of the release process by using ProjectIC's pre- and post-release hooks. In the example below, the pre-release hook runs a compilation check to make sure that the released files compile.

Once the release is created, the contributor can then mark this release as 'SOC\_READY' for integration. Note that this release was 'coco.CPU\_Core@9.TRUNK'.

```

[contributor] pi ip aliasset coco.CPU_Core@9.TRUNK SOC_READY Success, alias 'SOC_READY' set on 'coco.CPU_Core@9.TRUNK'.

```

Now, the integrator can query his workspace to find out if there are any new releases available for integration.

```

[integrator] pi workspace status -v

Workspace ID: 20

Directory: /home/mdx/workspaces/s1

```

IP: lib.soc\_integ@4.TRUNK

Resources:

| -1  | Name                             | 1 | Expected Version | 1 | Local Version | ı | WS | Status | ı | Server Status  | 1 | Mode      | ı |

|-----|----------------------------------|---|------------------|---|---------------|---|----|--------|---|----------------|---|-----------|---|

| - 1 | lib.soc_integ                    | - | 4.TRUNK          | 1 | 4.TRUNK       | 1 |    | OK     | - | New Resources  | - | Container | - |

| - 1 | IEC_ARM_coco.SY750               | - | 5.TRUNK          | 1 | 5.TRUNK       | 1 |    | OK     | - | OK             | - | Refer     | - |

| - 1 | Memories.CS-TS28N-GS-1PSRM       | - | 5.TRUNK          | 1 | 5.TRUNK       | 1 |    | OK     | - | OK             | - | Refer     | - |

| - 1 | coco.CPU_Cache                   | - | SOC_READY.TRUNK  | 1 | 8.TRUNK       | 1 |    | OK     | - | OK             | - | Refer     | - |

| - 1 | coco.CPU_Core                    | - | SOC_READY.TRUNK  | 1 | 8.TRUNK       | 1 |    | OK     | - | New @SOC_READY | - | Refer     | - |

| - 1 | coco.CPU_Logic                   | - | 6.TRUNK          | 1 | 6.TRUNK       | 1 |    | OK     | - | OK             | - | Refer     | - |

| R   | Recommendation: Update spark.soc |   |                  |   |               |   |    |        |   |                |   |           |   |

As can be seen from the output of the workspace status command, the integrator has the indication that a new component IP is available for integration. This workspace can now be updated using the projectIC update commands to bring in this new release into the workspace.

Either as part of the update process (using the post-update hook), or as a separate step, the integrator can run her integration checks. These checks are typically run as tests at the top level. Depending on the results of these tests, the integrator can mark this new configuration as 'GOLD', or leave the previous configuration as 'GOLD'.

In the example below, some tests are run as part of the update step (using the post-update hook on lib.soc integ) and as a result, the IP is automatically checked for integration issues and qualified.

```

Fintegrator  pi update

INFO:pi:Updating workspace to LATEST. For large IPs this could take a while.

: Preparing update ...

: Reading BOM: /home/mdx/workspaces/s1/.methodics/ws.bom

: Setting up jobs for 2 IPs

INFO

INFO

: Submitted 2 server jobs

TNFO

: Waiting for 2 server jobs

INFO

: - use Ctrl-C to stop waiting: the jobs will keep running

TNFO

: Server jobs done

----- SUMMARY -----

RELEASE SERVER JOB LOCAL JOB MODE RELPATH

BLOCK

coco.CPU_Cache SOC_READY success

refer coco.CPU_Cache

None

None

coco.CPU_Core SOC_READY success

refer coco.CPU_Core

2 server jobs succeeded

INFO:pi:Calling post-update hook for spark.soc@4.TRUNK

/mdx_local/tools/scripts/integ_check

INFO:pi:

Running Integration Tests...

Tests complete!

Results:

Total tests: 10

Tests Run: 9

Tests Passed: 9

Tests Failed: 0

Integration Passed!

Setting 'GOLD' on coco.CPU_Cache@8.TRUNK...

Setting 'GOLD' on coco.CPU_Core@9.TRUNK...

Update summary:

New

coco.CPU Core

SOC_READY.TRUNK [@8] SOC_READY.TRUNK [@9]

```

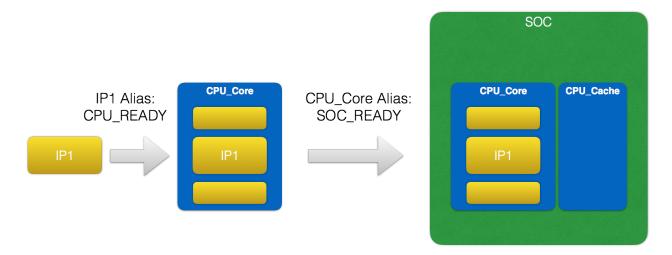

# **Hierarchical Integration**

Integration can be performed at any level. For example, if coco.CPU\_Core has IPs of its own, then contributors can release IPs to be integrated into lib.CPU\_Core using a similar scheme. Once new IPs are integrated into lib.CPU\_Core, the resulting release can be marked for integration at the SoC level and so on.

Each IP and sub-system can define its own 'ready for integration' aliases. An example is shown below:

As shown, an IP (IP1) can be integrated by the CPU\_Core, which in turn can be integrated into the SoC - all of this is done using the moving aliases flow described above.

For more information on this topic, or on any of Methodics products and solutions, please email <a href="mailto:contact@methodics.com">contact@methodics.com</a>.